DESIGN NOTE #028

Author: Chris R. Morse, chris@morsetech.net Keywords: External SRAM Small AVR, XRAM

This document is originally distributed by AVRfreaks.net, and may be distributed, reproduced, and modified without restrictions. Updates and additional design notes can be found at: www.AVRfreaks.net

## Using External SRAM with Small AVR Devices

**Introduction** When using small AVR devices, internal SRAM is often limited and there are insufficient I/O pins to interface with an external memory (SRAM) device. This article examines a few ways one may overcome this limitation and provides a schematic/figure and code for one such method. The intention is not to provide a full working solution, although one is provided, but to provide a background of ideas to explore and allow the designer to choose from more options to create the solution that works best for the application at hand.

**Background** Before discussing how to design an application to use external memory, it is helpful to examine how memory is typically used and accessed in embedded applications.

First, let us examine how memory is used. Most uses can be classified into three types of data: Operation, configuration, and storage. Operation data consists of items such as local variables, pointers, and the call stack. Configuration data consists of general parameters for operation and user or state defined values. This type of data is usually seen as blocks of fields (structures or "structs" in C) and is often used to initialize operation data. Storage is usually the input and/or output of the embedded system, for example: The conversion values of Analog to Digital Converters (ADC).

Second, we shall consider what type of memory addressing is necessary. Without hesitation, most designers would say direct random access is required. However, many embedded applications can be very effective, more efficient even, using other modes such as sequential addressing. Even those applications that truly require random access can often be reasonably accommodated with careful design.

The Challenge of<br/>Interfacing with<br/>External MemoryThe challenge to using external memory comes down to basic economics-scarcity.<br/>Microcontrollers have a limited number of I/O pins and memory devices require an<br/>abundance of them, particularly for addressing. By using some of the address circuits<br/>described below it is possible to use external memory with small AVR devices such as<br/>the AT90S2313.

Traditionally, address lines are multiplexed using latches such as the 74HC573 family or sometimes a Shift Register. An alternate method is to use a Ripple Counter like the CD4040BC family. A Ripple Counter approach (described below) can address an unlim-

ited amount of SRAM using only two pins. Table 1 below compares these methods for I/O pin requirements and addressing speed.

| Interface Method | I/O Pin Requirements | Address Access Speed                    |

|------------------|----------------------|-----------------------------------------|

| Direct           | Very high            | Very fast                               |

| Latch            | High                 | Fast                                    |

| Shift Register   | Medium               | Slow                                    |

| Ripple Counter   | Very low             | Fast (sequential)<br>Very slow (random) |

Table 1. Comparison of External Memory Address Interfaces

## Design Using Ripple Counters

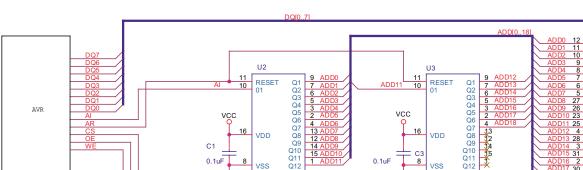

| Hardware          | The hardware design for using Ripple Counters (also called Ripple Carry Binary Counters) is straightforward. The Ripple Counter requires a ripple input (AI) and a reset pin (AR). Both pins are used together by the application to control addressing. The AI pin increments the address (sequentially) and AR resets it to zero.<br>One can accommodate more address lines than available in a single Ripple Counter device by "daisy-chaining" the devices together. To do so, connect the most significant                                                                                                                                                                                                                       |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                   | bit (MSB) of the first device to the input pin of the next device and so on for as many devices as necessary. Figure 1 below shows this circuit with U3 being incremented by U2, in effect; this adds an additional decade to the counter circuit. This entire circuit requires only 13 pins to address, control, and read/write data to the SRAM device. By comparison, using a Shift Register would require 17 pins and a typical latch circuit would require at least 21 pins and would be limited to addressing 16 lines ( $2^{16} = 64$ KB). For additional pin savings on either circuit a bi-directional Shift Register could be used for the data pins however, there is much more overhead in data access using this method. |  |

| Firmware/Software | No matter what circuit is used, the application should be designed to make optimal use<br>of the addressing scheme employed. To do this successfully, the data must be parti-<br>tioned. Operational data should almost always be stored in the fastest, most local<br>memory, in this case, the AVR internal SRAM. Conversely, configuration and storage<br>data can usually be moved to external memory. When using sequential addressing,<br>items accessed frequently should be placed at the lowest addresses.                                                                                                                                                                                                                   |  |

|                   | The example code below illustrates how to access the SRAM using the circuits shown in Figure 1. In data-logging type applications this is a very effective solution that provides fast access time and leaves enough device pins to accomplish the purpose of the application.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Enhancements      | <ul> <li>An enhancement for this scheme could be to make the most significant one or two address lines separately controlled by dedicated I/O pins, effectively making banks or pages in the SRAM. Doing so would have two benefits:</li> <li>1. Reduce the amount of time to access higher addresses and</li> <li>2. Reduce the amount of code required by using a smaller variable size for the tRamSize type.</li> </ul>                                                                                                                                                                                                                                                                                                           |  |

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 A18

4 28

22 24 29 CS1 OE WE

SRAM

I/O1 I/O2 I/O3 I/O4 I/O5 I/O6 I/O7 I/O8

20 21

32 vcc

16 VSS

VCC

C2 0.1uF

## **Summary**

AVR

This article has illustrated a few ways that AVR microcontrollers can interface with external SRAM using very few I/O pins and not sacrifice much functionality or performance. Hopefully, it has provided some new ideas for interfacing external memory with small AVR devices.

vcc

0.1uF

16

C3

8

VDD

CD4040BC

13245

13

Q12

Figure 1. Interface to External SRAM Using Ripple Counters for Address Lines

vçc 16

C1

0.1uF

VDD

vss

CD4040BC

8

| Example Code |                                               |                 |

|--------------|-----------------------------------------------|-----------------|

|              | /*****                                        |                 |

|              | * File: SRAMlib.c                             |                 |

|              | * Author: Chris Morse, chri                   | s@morsetech.net |

|              | * Purpose: Interface to JDEC standard         |                 |

|              | * SRAM chips                                  |                 |

|              | ******                                        |                 |

|              | <pre>#include <io-avr.h></io-avr.h></pre>     |                 |

|              | <pre>#include <inttypes.h></inttypes.h></pre> |                 |

|              | <pre>#include <pgmspace.h></pgmspace.h></pre> |                 |

|              | <pre>#include <iomacros.h></iomacros.h></pre> |                 |

|              |                                               |                 |

|              | //Change this for smaller addresses           |                 |

|              | typedef unsigned long tRamAddr;               |                 |

|              |                                               |                 |

|              | //Stores current address on counters          |                 |

|              | static tRamAddr glAddr;                       |                 |

|              |                                               |                 |

|              | //These define how the sram is wired          |                 |

|              | <pre>// and can be in a project header</pre>  |                 |

|              | #define SRAM_DATA_DDR                         | DDRB            |

|              | #define SRAM_DATA_OUT                         | PORTB           |

|              | #define SRAM_DATA_IN                          | PINB            |

|              | #define SRAM_SCS_PORT                         | PORTD           |

|              | #define SRAM_SCS_PIN                          | 2               |

|              | #define SRAM_SOE_PORT                         | PORTD           |

|              |                                               |                 |

```

#define SRAM SOE PIN

3

#define SRAM SWE PORT

PORTD

#define SRAM SWE PIN

4

#define SRAM_SAR_PORT

PORTD

#define SRAM SAR PIN

5

#define SRAM SAI PORT

PORTD

#define SRAM SAI PIN

6

//Macros for SRAM Control

//Put chip in Write mode

#define SRAM_SET_WRITE() { \

sbi(SRAM SOE PORT, SRAM SOE PIN); \

cbi(SRAM SWE PORT, SRAM SWE PIN); \

SRAM DATA DDR = 0xFF; }

//Commit Write to device

#define SRAM_COMMIT_WRITE() { \

sbi(SRAM SWE PORT, SRAM SWE PIN); \

cbi(SRAM_SWE_PORT, SRAM_SWE_PIN); }

//Set to Write mode and output

#define SRAM_SET_READ() { \

cbi(SRAM_SOE_PORT, SRAM_SOE_PIN); \

sbi(SRAM_SWE_PORT, SRAM_SWE_PIN); \

SRAM_DATA_DDR = 0x00; }

//Make sure SRAM is in wake mode

#define SRAM SELECT() \

cbi(SRAM SCS PORT, SRAM SCS PIN);

//Put the SRAM in standby

#define SRAM_DESELECT() \setminus

sbi(SRAM SCS PORT, SRAM SCS PIN);

//Reset the address latch

#define SRAM ADDR RESET() { \

sbi(SRAM_SAR_PORT, SRAM_SAR_PIN); \

cbi(SRAM_SAI_PORT, SRAM_SAI_PIN); \

cbi(SRAM_SAR_PORT, SRAM_SAR_PIN); }

//Increment the address latch

#define SRAM ADDR INCR()

{ \

sbi(SRAM_SAI_PORT, SRAM_SAI_PIN); \

cbi(SRAM SAI PORT, SRAM SAI PIN); }

//Functions for SRAM Actions

void SRAMsetAddr(const tRamAddr clAddr)

```

www.AVRfreaks.net

```

tRamAddr iIncUnits;

//Determine how much to increment

if(glAddr < clAddr) {

SRAM_ADDR_RESET();

iIncUnits = clAddr;

} else {

iIncUnits = clAddr - glAddr;

}

//Increment the adddress latch

while(iIncUnits--) {

SRAM ADDR INCR();

}

//Store the new adddress

glAddr = clAddr;

}

void* SRAMreadBuf(void* pbBuf, const tRamAddr clAddr, uint16_t ciSize)

{

uint8_t* pData = (uint8_t*)pbBuf;

//Setup the chip

SRAMsetAddr(clAddr);

SRAM SELECT();

SRAM_SET_READ();

//Read the data

while(ciSize > 0) {

//Copy byte to memory pointer

*pData = SRAM DATA IN;

SRAM_ADDR_INCR();

//Increment pointer and decr counter

pData++;

ciSize--;

}

SRAM_DESELECT();

return(pbBuf);

}

void SRAMwriteBuf(const tRamAddr clAddr, const void* const cpbBuf, uint16 t

ciSize)

{

uint8_t* pData = (uint8_t*)cpbBuf;

```

```

//Setup the chip

SRAMsetAddr(clAddr);

SRAM SELECT();

SRAM_SET_WRITE();

//Write the data

while(ciSize > 0) {

//Write data and commit

SRAM_DATA_OUT = *pData;

SRAM_COMMIT_WRITE();

//Increment the address & pointer % \left( {{\left( {{{\left( {{{\left( {{{\left( {{{{\left( {n} \right)}}} \right.}} \right.}} \right)}_{n}}} \right)}_{n}} \right)} \right)

SRAM_ADDR_INCR();

pData++;

//{\tt Decrement} the byte counter

ciSize--;

}

SRAM DESELECT();

```

}